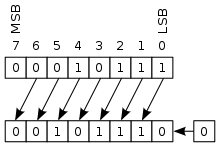

Un décalage logique consiste à supprimer un bit d'un côté de la suite de bits pour le remplacer par un zéro de l'autre côté.

00010111 (+23) LEFT-SHIFT = 00101110 (+46)

On note que sur une architecture de taille figée, le bit de poids fort peut être perdu (dépassement de capacité), et donc le résultat incorrect si l'on souhaitait réaliser une multiplication par deux. De plus, si le complément à deux est utilisé pour représenter les nombres négatifs, le bit de signe peut être altéré, donnant un résultat de signe opposé à l'opérande :

10110111 (-73) LEFT-SHIFT = 01101110 (+110)

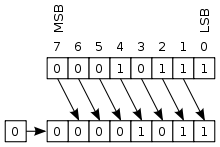

Le décalage à droite représente une division entière par 2. Si le bit de poids faible est à 1, c'est-à-dire que le nombre est impair, celui-ci sera perdu, conformément au principe de la division entière dans laquelle il ne peut pas y avoir de partie fractionnaire.

00010111 (+23) RIGHT-SHIFT = 00001011 (+11)

source : wikipedia  (

Christophe Béasse - Février 2019 )

(

Christophe Béasse - Février 2019 )